Všechny předchozí pokusy

s generováním jednoduchých obrazců na TFT sloužily pouze k ověření komunikace s TFT.

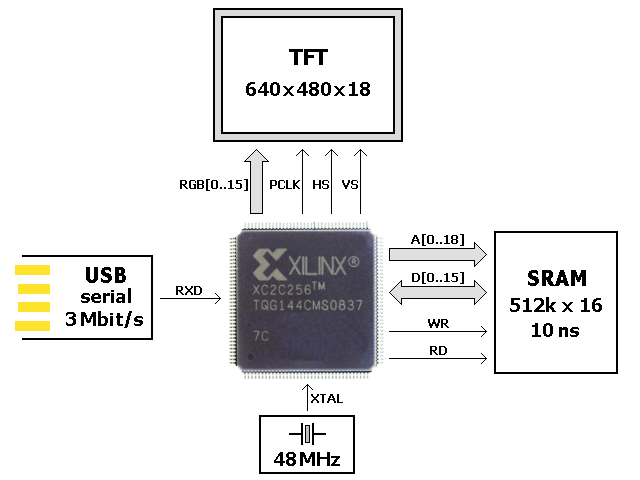

Hlavní záměr ovšem byl navrhnout pro tento TFT display kompletní řadič s video-RAM.

Protože se mi na první pokus nechtělo drátovat s paralelní sběrnicí k jednočipu, pořešil jsem

pro začátek zápis obrazových dat přes sériovou linku, se kterou se celkem pohodlně pracuje.

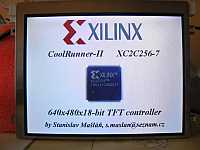

Jako CPLD jsem použil opět XC2C256-7 na kitu Xilinx XC2-XL od Digilentu.

|

|

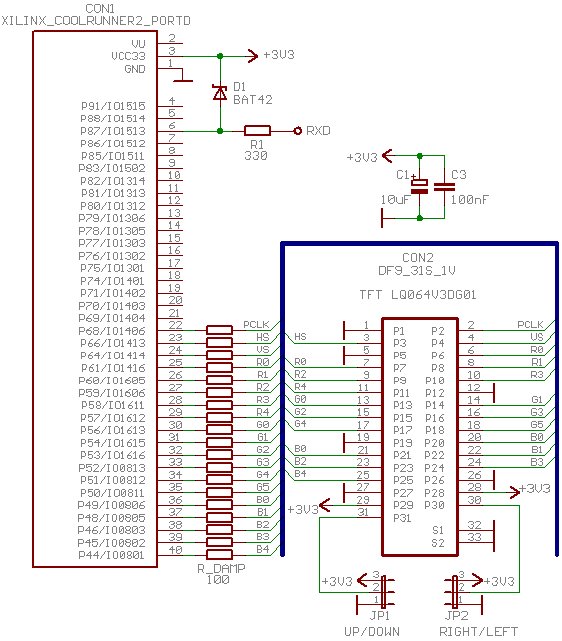

640x480x18-bit TFT modul je připojen stejně, jako byl minule, tj. přes 100R tlumící rezistory na portu D. Jejich hodnota závisí na délce a typu káblíku k TFT, ale bez nich to téměř jistě nepůjde, protože hrany z CPLD mají příliš vysokou strmost.

|

TFT modul je připojen se statickým ENABLE signálem, takže viditelná oblast modulu začíná

na pevné pozici dle datasheetu (pomocí tohoto signálu lze posouvat začátek řádků). Protože paměť je stejně jen

16-ti bitová, je display připojen jen v 16-bit módu.

Vzhledem k tomu, že CoolRunner 2 nemá 5V tolerant vstupy (rozdíl proti XC9500 sérii!),

je sériový vstup RXD ošetřen odporem a diodou, jak je

doporučeno v aplikačních poznámkách. Pro 3V3 logiku je to sice zbytečné, ale nepřekáží to.

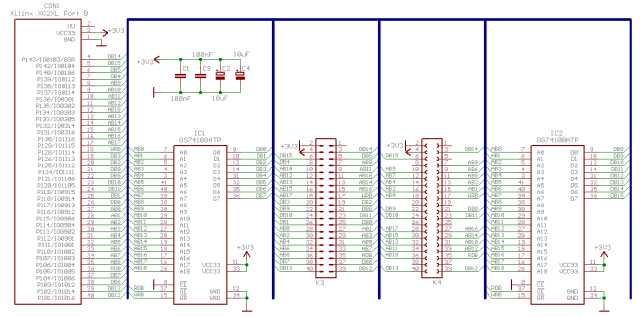

640x480 obrázek v 16-bit barvách vyžaduje 600kiB paměti, takže jsem vybral dvojici 8-bit SRAM 512kB zapojenou jako 512k x 16-bit. Rychlost jsem volil 10ns, protože pomalejší modely nejsou o moc levnější a časování by bylo podstatně náročnější. Paměť je připojena na portu B, kde je minimum speciálních pinů (jen jeden GSR).

|

Vzhledem k tomu, že jsou paměti připojené krátkými spoji, obešlo se to tentokrát

bez tlumících rezistorů.

Výkresy RAM modulu ke stažení:

osazení top,

bottom,

DPS top,

bottom.

Nabízí se v podstatě dvě možnosti, jak řadič realizovat. Ta primitivnější varianta předpokládá

použití dvou zcela oddělených RAM pamětí, kdy je jedna používána pro obnovování TFT a do druhé je možné libovolně

zapisovat/číst. Pak lze jednoduše řídícím signálem obě paměti prohodit (double buffering).

Výhodou této koncepce je jednoduchá struktura v hradlovém poli a rychlá komunikace s procesorem bez nutnosti používat WAIT signál.

Nevýhoda ovšem je potřeba dvou RAM a hlavně PLA s velkým počtem I/O a ty jsou dost drahé.

Druhou možností je použít sdílenou RAM v časovém multiplexu, kdy je polovina cyklu vyhrazena na obnovování TFT a

druhá polovina pro zápis nových dat. Výhodou je možnost použít celkem malé PLD s jedinou RAM, ale za cenu poměrně složité vnitřní

struktury s obtížným časováním. Navíc zápis dat je možný maximálně s taktem TFT, tj. pro 640x480 cca 25MB/s bez WAIT signálu.

Původně jsem sice předpokládál první variantu (proto je na fotkách dvojitý RAM modul), ale

povedlo se mi vyřešit problémy s časováním, takže řadič bez obtíží pracuje v multiplexu.

|

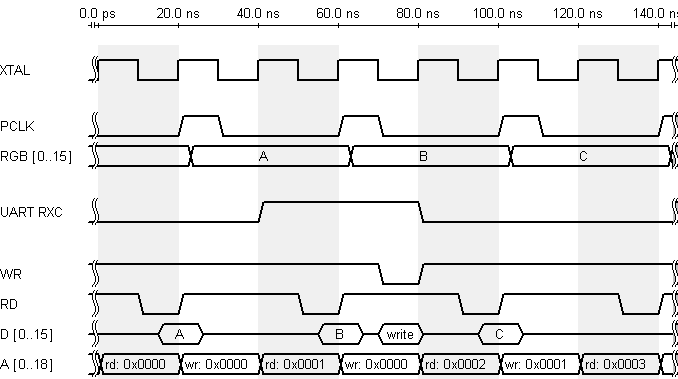

Časování jak by teoreticky mělo vypadat, ukazuje následující graf.

|

Jak vypadá časování ve skutečnosti netuším (a raději to snad ani nechci vědět), ale komunikace se zdá být bez chyb.

Považuji to docela za úspěch, protože takt paměti je v tomto uspořádání špičkově cca 50MHz (polovina její propustnosti) a to je,

vzhledem k primitivnímu dvou-fázovému časování, docela dobrý výsledek. Pro finální verzi, bude-li nějaká, by ale asi

bylo rozumné používat jemnější dělení cyklu, tj. ideálně 100MHz master clock.

Jak už jsem zmínil v úvodu, tak pro začátek je zápis obrazových dat řešen po sériové lince. Takt je nastaven na

3Mbit/s (maximum pro FT232), ale mohlo by to fungovat ještě i při 12Mbit/s. Jakmile dojde k příjmu dvou bytů (jeden pixel),

je po jeden cyklus vygenerován RXC signál a při průchodu zápisovým půlcyklem RAM dojde k uložení přijatého pixelu a inkrementaci adresy.

Protože se mi nechtělo řešit reset adresy tlačítky, doplnil jsem cca 500ms timeout, po kterém je zápisová adresa

automaticky vynulována a je možné zapsat nový snímek.

Součástí přiloženého zipu jsou i dvě utilitky. Jedna slouží pro převod 24-bit BMP do RAW 565 se kterým

řadič pracuje a druhá je

jednoduchý konzolový terminálek pro odesílání souborů na zvolený port zadanou rychlostí (víc neumí).

Zdrojáky ke stažení: CoolRunner2_TFT_serial.zip (1524kB).

Pár fotek, jak to vypadá za chodu:

|

|

|

|

A malá video ukázka:

| Last update: 4.6.2012 |  |

|